August 13, 2025 Sheraton Grand Bengaluru

Registration opens on July 14, 2025

Cancelling your registration will remove your access to the event. If you proceed, you will no longer be able to participate or access event-related materials.

Deleting your account will remove your access to the event.

Registration opens on July 14, 2025

August 13, 2025

13-08-2025 09:30 am

13-08-2025 09:30 am

Prateek Omer

Google India

Sachin Waghmare

Google India

13-08-2025 10:00 am

13-08-2025 10:00 am

Prashant Kumar Vallbhabhai Bhut

Broadcom

13-08-2025 10:30 am

13-08-2025 10:30 am

Amrut Grampurohit

MediaTek

Kishore YC

MediaTek

13-08-2025 02:15 pm

13-08-2025 02:15 pm

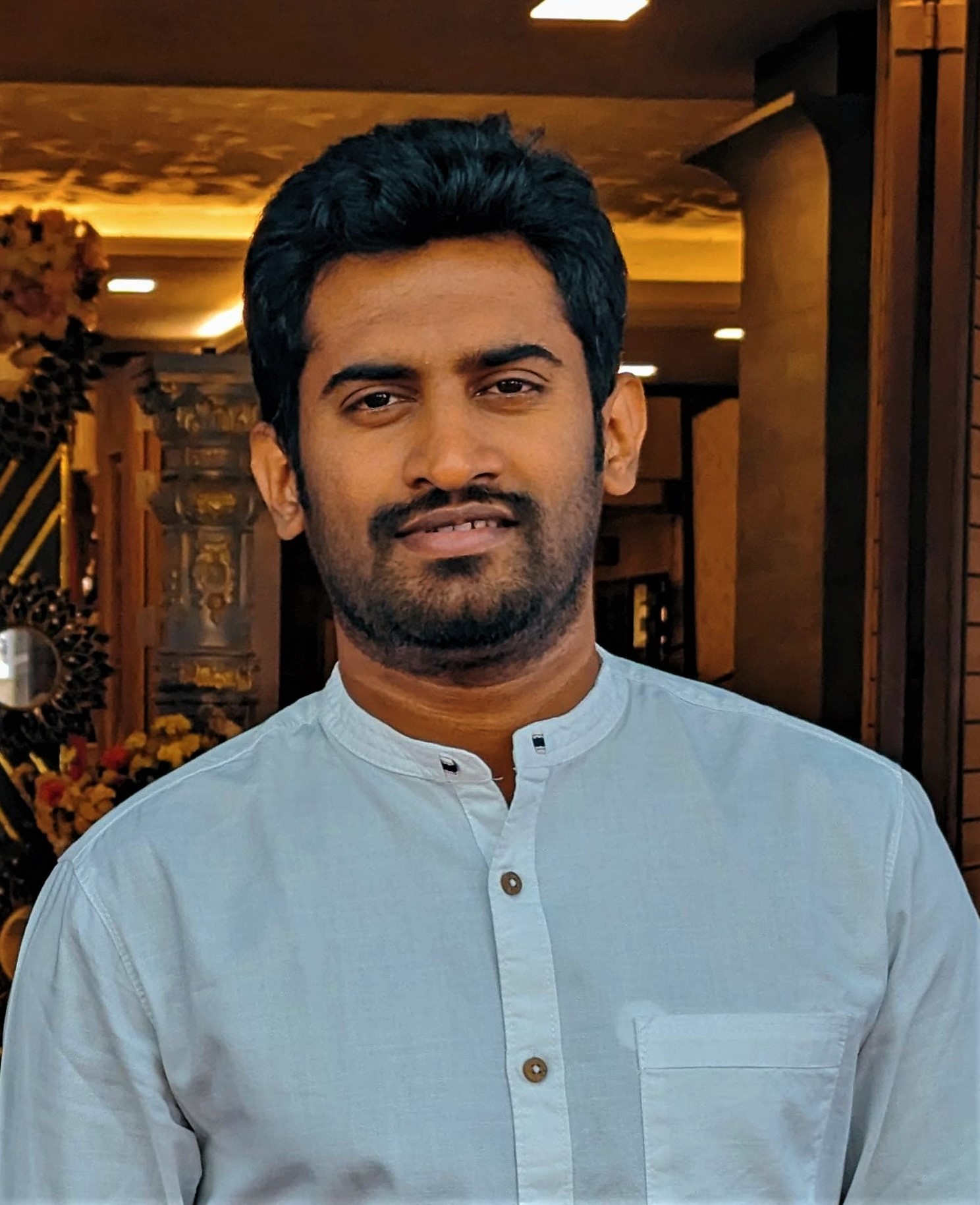

Rahul Singh

Samsung

Rahul Singh, Staff Engineer specializing in Physical Design at Samsung Semiconductors India Research.

With 8 years of dedicated experience in the semiconductor industry, Rahul has expertise in optimizing complex SoC designs and ensuring robust performance for mobile processors and automotive SoCs.

His career spans significant roles at Wipro Limited and Waferspace , working for a diverse portfolio of tier-one clients including Intel, Qualcomm, Google, and Texas Instruments.

Anil Kumar Swain

Samsung

Anil is a Physical design engineer at Samsung Semiconductor India, specializing in advanced design optimization techniques using Cadence, synopsys tools, and Tcl scripting. He leverages innovative methodologies, thereby enhancing chip performance and efficiency for next generation semiconductor technologies.

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Shvetha Natarajan

Analog Devices

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Rajeev Mishra

Qualcomm

Talawara Manjunath

Qualcomm

sonu Nehra

Qualcomm

Nitin Kaushik

Qualcomm

Almost 2 Decade of semiconductor industry Experience with SOC chips catering to Auto/Mobile/Compute

Shammi Kumar

Qualcomm

I am Shammi Kumar I hold a degree in Electronics and Communication Engineering (ECE) and currently work in the implementation team, specializing in Synthesis (Synth), Logic Equivalence Checking (LEC), and Static Timing Analysis (STA). With a strong foundation in digital design and timing closure, I contribute to delivering high-quality, timing-optimized designs in the semiconductor domain. My role involves close collaboration with cross-functional teams to ensure design integrity and performance throughout the implementation flow.

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Deep Kalola

Samsung Semiconductor India Research

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Amogh KM

Rambus

Lakshman Kalpathy V

Rambus

Physical Design Engineer with 7+ years of Experience. Holds Masters in VLSI Design from Anna University, Chennai and have bachelor's from Cochin University of Science & Technology

Dinesh Kumar Gangatharan

Rambus

Sai Sumukha K V

Rambus

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Bala Subrahmanyam

Texas Instruments

13-08-2025 05:30 pm

13-08-2025 05:30 pm

SAI KRISHNA KAIRAMKONDA

intel

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Eswar Pentakota

Texas Instruments

I'm a Digital Design Engineer at Texas Instruments with a background in embedded systems and VLSI. After graduating in 2020, I worked at Hyundai, then completed my MTech from NIT Calicut. I enjoy working on semiconductor innovations. Outside work, I love watching movies and exploring new places.

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Abhishek Chouksey

Intel

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Chaitanyh Singh

Advanced Micro Devices

Akhilesh Reddy Gillela

AMD India Pvt Ltd

Anandhan M

AMD

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Sujeet Maurya

Texas Instruments India Pvt. Ltd.

Vishal Diwan

Texas Instruments

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Sneha Biswas

Intel

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Talawara Manjunath

Qualcomm

13-08-2025 05:30 pm

13-08-2025 05:30 pm

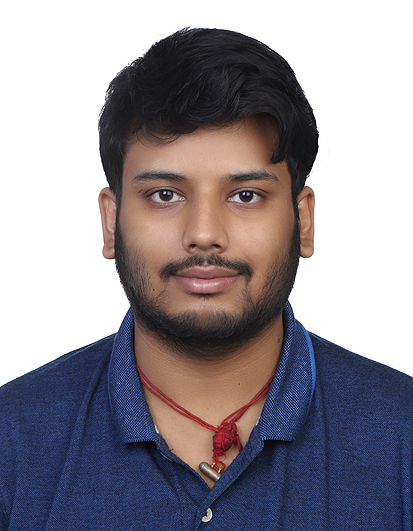

Yadukrishnan Gopinathan

Microchip

Yadukrishnan Gopinathan is a Digital VLSI specialist holding a Master’s degree in Digital VLSI Design from Amrita Vishwa Vidyapeetham, earned in July 2022. With 4 years of industry experience, including 3 years dedicated to the Design For Testability (DFT) domain, Yadukrishnan possesses expertise in Digital ICs, System Design, and Signal Processing. His skillset includes Scan Insertion, ATPG, Simulation, and Advanced fault modeling. He previously worked as a Silicon Design Engineer at Advanced Micro Devices (AMD) for 2.5 years and currently works as a Design Engineer specialized in Design for Testability at Microchip Technology Inc.

Adennagari Subramanyam

Microchip pvt ltd

13-08-2025 09:30 am

13-08-2025 09:30 am

Alok Chandra

Cadence

Kiran Patil

Cadence Design Systems

ANKIT FARKYA

Cadence Design Systems

13-08-2025 10:00 am

13-08-2025 10:00 am

Kumar Shubham

qualcomm

Prathamesh Pathak

Qualcomm

Mahesh Yatagiri

Qualcomm

13-08-2025 10:30 am

13-08-2025 10:30 am

Sanjit Sharma

RIVOS

I have over 14yrs of experience working in the backend design of ASIC chips. I have worked with Qualcomm, ARM , INTEL and Synopsys in my past.

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Praphulla Pandey

Google

Vaibhav Gupta

Google

Abhishek Kamath

Google

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Sabya Sachi Sahu

Samsung Semiconductor India Research

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Sridhar M V

Samsung Semiconductor India Research

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Ankit Gupta

Qualcomm

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Vidushi Gaur

Texas Instruments

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Usha KJ

Cadence

Aditya Chaudhary

Cadence

13-08-2025 05:30 pm

13-08-2025 05:30 pm

13-08-2025 09:30 am

13-08-2025 09:30 am

PRIYANKA SHARMA

Intel Technology India Pvt. Ltd.

Rahul Hebbar P R

INTEL

Likesh Sahoo

Cadence

Engineering Manager with 13+ years of experience in semiconductor process design kits (PDKs), CAD and EDA tool integration, Application Engineer and team leadership. Proven expertise in developing and validating PDKs for advanced nodes, managing cross-functional teams, and delivering high-quality solutions for IC design.

13-08-2025 10:00 am

13-08-2025 10:00 am

Priya Meharde

STMicroelectronics Pvt. Ltd.

13-08-2025 10:30 am

13-08-2025 10:30 am

Priyanka Madaan

NXP India Pvt. Ltd.

Akshita Bansal

Cadence Design Systems

Working as Lead Application Engineer for Custom layout design

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Shikha Prajapati

STMicroelectronics

Working as a Senior design Engineer in STMicroelectronics. Passionate VLSI engineer with over 8 years of experience in industry-leading projects and technologies. Experienced Design Engineer with a demonstrated history of working in the semiconductors industry. Skilled in Design Rule Checking (DRC), Layout verses Schematic (LVS), EM & IR and Antenna check. Application-Specific Integrated Circuits (ASIC), Very-Large-Scale Integration (VLSI), Physical Verification, and Integrated Circuits (IC), Analog layout.

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Arup Ray

Qualcomm India Private Limited

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Akshita Bansal

Cadence Design Systems

Working as Lead Application Engineer for Custom layout design

Mohit Chugh

NXP India Pvt. Ltd.

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Danish Shaikh

Western Digital Corporation

Sana .

Sandisk

13-08-2025 04:30 pm

13-08-2025 04:30 pm

SRINIVASU PARLA

Intel Technology India Pvt Ltd

13-08-2025 05:00 pm

13-08-2025 05:00 pm

SPOORTHI S S

Samsung Semiconductors

Krutarth Vegad

Cadence Design Systems

Laya Valsaraj

Cadence Design Systems

Wasimahmed Bepari

Samsung Semiconductor India Research (SSIR)

13-08-2025 05:30 pm

13-08-2025 05:30 pm

Satish Kumar Beja

Qualcomm

Neha Raskar

QUALCOMM INDIA

13-08-2025 09:30 am

13-08-2025 09:30 am

Sainath Karlapalem

NXP

Technical Director and Verification Competence Manager. Over 24 years of experience in field of Semiconductor design, verification and worked across multiple and diverse products

Atishkumar Savale

NXP Semiconductors

13-08-2025 10:30 am

13-08-2025 10:30 am

SACHIN S

STMicroelectronics

Nishant Kaundal

STMicroelectronics

Nishant Kaundal has nearly 12 years of experience in Mixed Signal verification domain & has a good know-how of SoC architectures, ranging from Mixed-Signal IPs to complex SoC integration. He has multiple paper-publications to his name, won various awards for his technical contribution & piloted various methodologies during his professional career. He is currently working as SoC_AMS Verification Engineer in GPAM division, based out of Greater-Noida, India.

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Dr Javed GS

Intel Foundry

Shubham Sachdeva

Intel

Sukanta Saha

Intel

Anshaj Shrivastava

Intel

Sivaram N Krishna

Intel Technology

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Kanika Gupta

NXP Semiconductors

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Vaibhav Garg

STMicroelectronics

13-08-2025 04:00 pm

13-08-2025 04:00 pm

PAVAN VERNEKAR

Infineon Technology

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Sunny Sharma

Micron Technology Operations India LLP

NARENDRA MANCHINEELLA

Micron Technology Operations India LLP

Ravi Shekhda

Micron Technology Operations India LLP

Ronak Pandya

Micron Technology Operations India LLP

Ronak Pandya is Lead Physical Desing Engineer at Micron Technology, located in Bangalore. With 9 years of experience, Ronak specialize in Physical Desing of high-speed memory interface IP and controller. Before joining Micron, Ronak worked at Samsung Semiconductor, Invecas and earned a master's degree in VLSI Desing from Thapar University Patiala, Panjab.

13-08-2025 05:30 pm

13-08-2025 05:30 pm

Apala Kinkar

Intel

13-08-2025 09:30 am

13-08-2025 09:30 am

Krishnakant Patil

Samsung Semiconductor India Research center, India

13-08-2025 10:00 am

13-08-2025 10:00 am

Lawish Deshmukh

Renesas Electronics India Private Limited

13-08-2025 10:30 am

13-08-2025 10:30 am

Amresh Kumar Lenka

Samsung

I have 6 years of DV experience and am passionate about the latest methodologies in DV

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Subham Mohapatra

Texas Instruments

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Aishwarya Patil

Samsung Semiconductor India Research

Sushree Bandita Panda

SSIR

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Atiq Jamadar

Samsung Semiconductor India Research

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Siri Rajanedi

Analog Devices India pvt ltd

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Manikanta Gummadidala

Samsung Semiconductor India Research Bangalore

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Sarang J Menon

Texas Instruments

MV Mahadevan

Texas Instruments

Ayushi Bapna

Texas Instruments

13-08-2025 05:30 pm

13-08-2025 05:30 pm

Amey Telang

Samsung Semiconductor India

Sunil Shrirangrao Kashide

Samsung Semiconductor India

13-08-2025 09:30 am

13-08-2025 09:30 am

Meghvendra Sinh Rathod

Meta Platforms Inc

Shravani Kode

Meta

13-08-2025 10:00 am

13-08-2025 10:00 am

Sarvesh Tiwari

STMicroelectronics

13-08-2025 10:30 am

13-08-2025 10:30 am

Pamarthy Gopika Rani Alekhya

Analog Devices

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Madhav Boddhapu

Google

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Vivekananda Upadyaya P

Qualcomm India Pvt Ltd

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Gayathri Siva

MediaTak

I am Siva Gayathri, a Staff Engineer at MediaTek with 7 years of experience in Design Verification. Currently working on PCIe IP and SoC verification for ASIC projects.

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Jaswanth Kumar Reddy Ambhati

Texas Instruments

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Sanjana Jain

Qualcomm

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Abhishek Kulkarni

Samsung Semiconductor India Research

Abhishek Bidhan

Samsung Semiconductor India Research

Himanshu Chauhan

Samsung

Senior Staff Engineer

13-08-2025 05:30 pm

13-08-2025 05:30 pm

Gaurav Malik

Nvidia

13-08-2025 09:30 am

13-08-2025 09:30 am

Anirban Majumder

Google IT Services India Pvt Ltd

13-08-2025 10:00 am

13-08-2025 10:00 am

sooraj s

Samsung Semiconductor India Research

sreenivasulu Alamuri

SAMSUNG SEMICONDUCTOR INDIA RESEARCH

13-08-2025 10:30 am

13-08-2025 10:30 am

Saurav Chatterjee

STMicroelectronics

ASHUTOSH BISHT

STMicroelectronics

13-08-2025 02:00 pm

13-08-2025 02:00 pm

Parth Chokhawala

Meta Platforms Inc.

13-08-2025 02:25 pm

13-08-2025 02:25 pm

Bhanu Suprabhath G.V.N.S

Samsung

Bhanu leads the flagship Sub-System verification and validation aspects of Image signal Processing at SSIR. He has 5 years of experience working on conventional Design verification as well as emulation platform for camera.

13-08-2025 02:50 pm

13-08-2025 02:50 pm

Pranali Gaydhane

Texas Instruments

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Nidhi Makwana

Google

Preethi Ashok Kumar

Google

Ravi Mangal

Google India

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Chandra Gupta

Samsung

Sudhakar Bansal

Samsung

My name is Sudhakar Bansal, and I am currently working as a Director at SSIR(Samsung Semiconductor India Research), Banglore. I am passionate about functional verification, in-circuit emulation and task automation. With extensive experience in pre-silicon functional verification of about 18 years, I have worked for IP, Sub-system and SoC verification. I have a post-graduation degree from IIT-Roorkee with specialization in microelectronics.

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Alok Mistry

Google

Aditya Chitrode

Google India

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Sharon Ruth

Samsung

Sharon Ruth is a Staff Engineer at Samsung Semiconductor India Research with 7 years of experience in Design-for-test DFT methodologies. She specializes in ATPG pattern generation, post silicon debug, ensuring high test coverage and yield for complex semiconductor designs.

13-08-2025 05:30 pm

13-08-2025 05:30 pm

Vivek Gopalkrishna

Analog Devices

Vivek Gopalkrishna is a Senior verification engineer in the Engineering Enablement team at Analog Devices. He is responsible for exploring and deploying Emulation and Portable stimulus methodologies to projects across ADI. He joined Analog Devices in 2022 prior to which he worked for 2 years on similar domains of verification. He holds a B.E. degree in Electronics and Communication Engineering from BMS College of Engineering, Bangalore.

13-08-2025 09:30 am

13-08-2025 09:30 am

Sheetal Jain

Krutrim SI Designs

13-08-2025 10:00 am

13-08-2025 10:00 am

ABHISHEKH M L

Sandisk Technologies, Inc.

TAMILHARASAN M

Sandisk Technologies, Inc.

Vijay Kumar Singh

Sandisk Technologies, Inc.

13-08-2025 10:30 am

13-08-2025 10:30 am

Sivakumar NM

L&T Technology Services

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Santosh Bhagat

Cadence Design System

Gayetri Gayetri

Craftronics India Pvt Ltd

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Saurav Kumar

Lenovo

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Upender Dharavath

Micron Technology Operations India LLP

Nishtha Tiwari

Micron

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Santhosh Rangasamy

Infineon Technologies Semiconductor India Private

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Jayanth Venkatesh

MaxLinear Inc

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Kiran Kumar T

QUALCOMM

13-08-2025 02:15 pm

13-08-2025 02:15 pm

Suraj M

Intel

13-08-2025 02:45 pm

13-08-2025 02:45 pm

Hemant Wadhavankar

Lattice Semiconductor

Prakhar Nayak

Lattice Semiconductor India Pvt. Ltd.

13-08-2025 03:30 pm

13-08-2025 03:30 pm

Mallikarjun Baragali

Analog Devices

13-08-2025 04:00 pm

13-08-2025 04:00 pm

Himanshu Tanwar

Cadence Design Systems

13-08-2025 04:30 pm

13-08-2025 04:30 pm

Vedha S

Samsung Semiconductor India research

Sukruthi K

Samsung

13-08-2025 05:00 pm

13-08-2025 05:00 pm

Santhosh Kamatam

NXP semiconductor

Abhishek Kamath

Google

Krati Jain

Google

ganesh Andhavarapu

microsoft

GANESH ANDHAVARAPU

Microsoft

Giridhar Nagireddy

Texas Instruments

Priya Jindal

Texas Instruments

Tushar Tripathi

Texas Instruments India

Hariharan Ayappane

Texas Instruments Incorporated

Piyushkumar Chaniyara

Texas Instruments

Satish Sajjanar

Texas Instruments

SANDIP KUMAR

Cadence Design Systems

VIKRANT KHANNA

Cadence Design Systems

Isha Srivastava

Cadence Design Systems

Galina Ross

Samsung

Galina Ross is a senior analog layout engineer at Samsung, with deep expertise in managing high-performing layout teams and driving innovation in advanced semiconductor design.

Abraham George

Samsung